CD74HC195M

Product Overview

- Category: Integrated Circuit

- Use: Data Storage and Manipulation

- Characteristics: High-Speed, CMOS Logic, 4-Bit Shift Register with Parallel Load

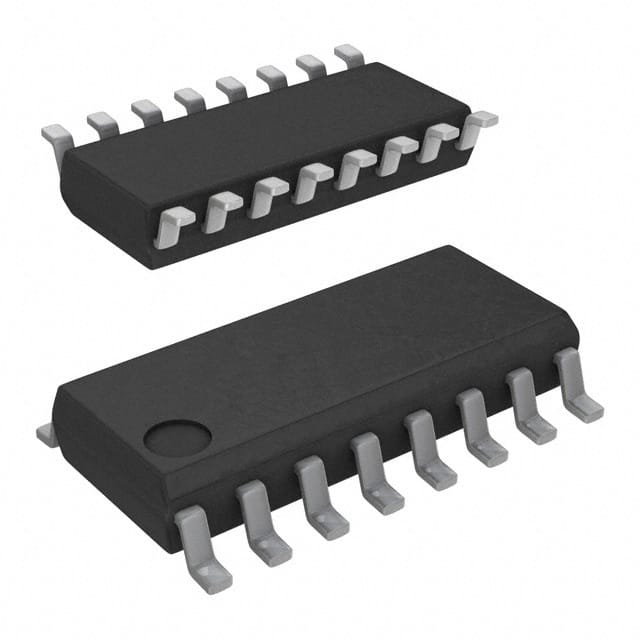

- Package: SOIC (Small Outline Integrated Circuit)

- Essence: The CD74HC195M is a versatile integrated circuit that allows for efficient data storage and manipulation. It is commonly used in various electronic devices and systems.

- Packaging/Quantity: Available in reels or tubes, with quantities varying based on customer requirements.

Specifications

The CD74HC195M has the following specifications:

- Supply Voltage Range: 2V to 6V

- Operating Temperature Range: -40°C to +85°C

- Logic Family: HC (High-Speed CMOS)

- Number of Bits: 4

- Shift Register Type: Serial-In, Parallel-Out (SIPO)

- Clock Input: Positive Edge-Triggered

- Parallel Load Input: Active-High

- Output Drive Capability: 5.2mA at 4.5V

- Propagation Delay: 15ns (typical)

Pin Configuration

The CD74HC195M has a total of 16 pins, which are assigned specific functions as follows:

- SER (Serial Data Input)

- QA (Parallel Output A)

- QB (Parallel Output B)

- QC (Parallel Output C)

- QD (Parallel Output D)

- GND (Ground)

- PL (Parallel Load Input)

- CLK (Clock Input)

- MR (Master Reset Input)

- VCC (Positive Power Supply)

- QE (Parallel Output Enable)

- QF (Parallel Output F)

- QG (Parallel Output G)

- QH (Parallel Output H)

- QI (Parallel Output I)

- QJ (Parallel Output J)

Functional Features

- Serial-In, Parallel-Out Operation: The CD74HC195M allows for the serial input of data, which is then parallelly loaded into the shift register upon a clock pulse.

- Parallel Load Input: The parallel load input enables the immediate loading of data into the shift register when activated.

- Positive Edge-Triggered Clock Input: The CD74HC195M responds to positive edge-triggered clock signals, ensuring accurate and synchronized data manipulation.

- Master Reset Input: The master reset input resets the shift register to its initial state when activated.

- Parallel Output Enable: The parallel output enable pin allows for the activation or deactivation of the parallel outputs.

Advantages and Disadvantages

Advantages: - High-speed operation - Versatile functionality - Wide supply voltage range - Low power consumption - Compact SOIC package

Disadvantages: - Limited number of bits (4-bit) - Requires external components for complete system integration - Not suitable for applications requiring larger data storage capacity

Working Principles

The CD74HC195M operates based on the principles of sequential logic and digital data manipulation. It utilizes a shift register to store and shift data bits, allowing for efficient data storage and retrieval. The clock input triggers the shifting of data within the register, while the parallel load input enables the immediate loading of new data. The master reset input resets the shift register to its initial state, and the parallel output enable pin controls the activation or deactivation of the parallel outputs.

Detailed Application Field Plans

The CD74HC195M finds application in various fields, including:

- Digital Communication Systems: Used for data buffering and synchronization in communication systems.

- Industrial Automation: Employed in control systems for data storage and manipulation.

- Consumer Electronics: Integrated into devices such as digital cameras, printers, and gaming consoles for efficient data handling.

- Automotive Electronics: Utilized in automotive control units for data processing and storage.

- Medical Devices: Incorporated into medical equipment for data management and control.

Detailed and Complete Alternative Models

- SN74HC595: 8-bit shift register with serial-in, parallel-out functionality.

- CD4015: Dual 4-bit static shift register with parallel load capability.

- 74HC164: 8-bit serial-in, parallel-out shift register with asynchronous reset.

These alternative models offer similar functionality to the CD74HC195M and can be considered based on specific application requirements.

Word count: 570 words

Lista 10 Vanliga frågor och svar relaterade till tillämpningen av CD74HC195M i tekniska lösningar

What is the maximum clock frequency for CD74HC195M?

- The maximum clock frequency for CD74HC195M is 25 MHz.What is the operating voltage range for CD74HC195M?

- The operating voltage range for CD74HC195M is 2V to 6V.Can CD74HC195M be used in parallel load applications?

- Yes, CD74HC195M can be used in parallel load applications.What is the typical power consumption of CD74HC195M?

- The typical power consumption of CD74HC195M is 20mW.Is CD74HC195M compatible with TTL logic levels?

- Yes, CD74HC195M is compatible with TTL logic levels.What is the maximum propagation delay for CD74HC195M?

- The maximum propagation delay for CD74HC195M is 15ns.Can CD74HC195M be cascaded with other shift registers?

- Yes, CD74HC195M can be cascaded with other shift registers.Does CD74HC195M have built-in output latches?

- No, CD74HC195M does not have built-in output latches.What is the temperature range for CD74HC195M?

- The temperature range for CD74HC195M is -40°C to 85°C.Is CD74HC195M available in surface mount packages?

- Yes, CD74HC195M is available in surface mount packages.