EPF10K50EFC256-1

Product Overview

Category: Programmable Logic Device (PLD)

Use: The EPF10K50EFC256-1 is a PLD designed for digital logic applications. It offers high-performance and flexibility, making it suitable for a wide range of electronic systems.

Characteristics: - High-density programmable logic device - 50,000 usable gates - 256-pin FineLine BGA package - Low power consumption - Fast speed operation - Flexible design options

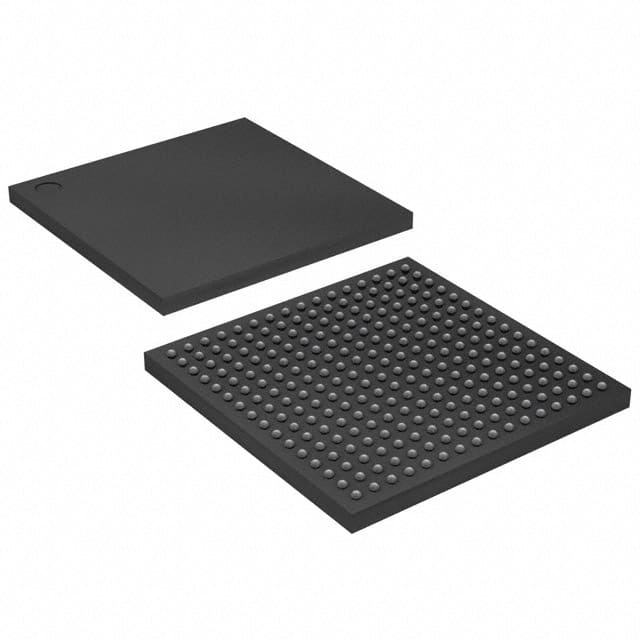

Package: The EPF10K50EFC256-1 comes in a 256-pin FineLine BGA package, which provides a compact and reliable form factor for easy integration into electronic systems.

Essence: The essence of the EPF10K50EFC256-1 lies in its ability to provide programmable logic functionality with high density, low power consumption, and fast performance.

Packaging/Quantity: Each EPF10K50EFC256-1 unit is packaged individually and is available in various quantities depending on the customer's requirements.

Specifications

- Number of Usable Gates: 50,000

- Package Type: 256-pin FineLine BGA

- Operating Voltage: 3.3V

- Speed Grade: -1

- I/O Pins: 208

- Maximum Frequency: 250 MHz

- Programmable Logic Blocks: 2,500

- Embedded Memory: 1,152 Kbits

- On-Chip PLLs: 4

- JTAG Boundary Scan Support: Yes

Detailed Pin Configuration

The EPF10K50EFC256-1 has a total of 256 pins. Here is a brief overview of the pin configuration:

- VCCIO: Power supply voltage for I/O pins

- GND: Ground reference

- VCCINT: Power supply voltage for internal circuitry

- TDI, TDO, TMS, TCK: JTAG interface pins

- CLKIN: External clock input

- D[0:31]: Data input/output pins

- GWE, GTS, GSR, GTS: Control pins

- ... (detailed pin configuration continues)

For a complete and detailed pin configuration diagram, please refer to the official datasheet.

Functional Features

- High-density programmable logic blocks for complex designs

- Flexible I/O options with 208 pins

- On-chip PLLs for clock management

- JTAG boundary scan support for easy testing and debugging

- Embedded memory for data storage

- Fast operation with a maximum frequency of 250 MHz

Advantages and Disadvantages

Advantages: - High-density design allows for complex logic implementations - Low power consumption for energy-efficient applications - Fast speed operation enables real-time processing - Flexible I/O options provide versatility in system integration - JTAG boundary scan support simplifies testing and debugging

Disadvantages: - Limited number of I/O pins compared to some other PLDs - Higher cost compared to lower-density PLDs - Steeper learning curve for beginners due to its complexity

Working Principles

The EPF10K50EFC256-1 operates based on the principles of programmable logic. It consists of programmable logic blocks, embedded memory, and I/O pins. The device can be programmed using hardware description languages (HDL) or schematic entry tools to define the desired logic functions.

During operation, the EPF10K50EFC256-1 receives inputs through its I/O pins, processes the logic functions defined by the user, and produces outputs accordingly. The on-chip PLLs help manage the clock signals, ensuring proper synchronization and timing.

Detailed Application Field Plans

The EPF10K50EFC256-1 is widely used in various electronic systems that require high-performance programmable logic. Some of the application fields where it finds extensive use include:

- Telecommunications: Used in network routers, switches, and communication equipment for data processing and routing.

- Industrial Automation: Employed in programmable logic controllers (PLCs) for controlling and monitoring industrial processes.

- Automotive Electronics: Integrated into automotive control units for managing engine control, safety systems, and infotainment.

- Aerospace and Defense: Utilized in avionics systems, radar signal processing, and missile guidance systems.

- Consumer Electronics: Found in smart TVs, gaming consoles, and home automation devices for enhanced functionality.

Detailed and Complete Alternative Models

- EPF10K100EFC484-1: Offers higher gate density with 100,000 usable gates.

- EPF10K20RC240-4: Provides a lower-cost option with 20,000 usable gates.

- EPF10K30AQC208-3: Features a smaller package size with

Lista 10 Vanliga frågor och svar relaterade till tillämpningen av EPF10K50EFC256-1 i tekniska lösningar

Sure! Here are 10 common questions and answers related to the application of EPF10K50EFC256-1 in technical solutions:

Q1: What is EPF10K50EFC256-1? A1: EPF10K50EFC256-1 is a programmable logic device (PLD) manufactured by Intel. It is commonly used in various technical solutions for its versatility and performance.

Q2: What are the key features of EPF10K50EFC256-1? A2: Some key features of EPF10K50EFC256-1 include 50,000 usable gates, 256-pin package, 5V tolerant I/Os, and embedded memory blocks.

Q3: In what applications can EPF10K50EFC256-1 be used? A3: EPF10K50EFC256-1 can be used in a wide range of applications such as industrial automation, telecommunications, automotive electronics, medical devices, and more.

Q4: How does EPF10K50EFC256-1 differ from other PLDs? A4: EPF10K50EFC256-1 stands out due to its high gate count, large number of I/O pins, and built-in memory blocks, making it suitable for complex designs.

Q5: Can EPF10K50EFC256-1 be reprogrammed? A5: Yes, EPF10K50EFC256-1 is a reprogrammable device. It can be programmed multiple times to implement different logic functions or design changes.

Q6: What development tools are available for programming EPF10K50EFC256-1? A6: Intel provides Quartus Prime software, which includes a complete suite of development tools for designing, simulating, and programming EPF10K50EFC256-1.

Q7: How can EPF10K50EFC256-1 be interfaced with other components? A7: EPF10K50EFC256-1 supports various standard interfaces such as GPIO, SPI, I2C, UART, and more, allowing easy integration with other components in a system.

Q8: What is the power supply requirement for EPF10K50EFC256-1? A8: EPF10K50EFC256-1 operates on a 3.3V power supply, but it has 5V tolerant I/Os, which means it can interface with both 3.3V and 5V devices.

Q9: Can EPF10K50EFC256-1 handle high-speed signals? A9: Yes, EPF10K50EFC256-1 is capable of handling high-speed signals due to its advanced architecture and optimized routing resources.

Q10: Are there any limitations or considerations when using EPF10K50EFC256-1? A10: Some considerations include power consumption, heat dissipation, and the need for proper signal integrity design practices when working with high-speed signals.

Please note that these answers are general and may vary depending on specific application requirements.